# JEPPIAAR INSTITUTE OF TECHNOLOGY

"Self-Belief | Self Discipline | Self Respect"

DEPARTMENT

OF

# ELECTRONICS AND COMMUNICATION ENGINEERING

# LECTURE NOTES EC8351 – ELECTRONIC CIRCUITS 1 (Regulation 2017)

Year/Semester: II/03 2021 – 2022

Prepared by Ms.S.SUREKHA Assistant Professor/ECE

# **SYLLABUS**

## EC8351

# **ELECTRONIC CIRCUITS 1**

LTPC 3003

# **OBJECTIVES:**

- To understand the methods of biasing transistors

- To design and analyze single stage and multistage amplifier circuits

- To analyze the frequency response of small signal amplifiers

- To design and analyze the regulated DC power supplies.

- To troubleshoot and fault analysis of power supplies

## UNIT I BIASING OF DISCRETE BJT, JFET AND MOSFET

BJT-Need for biasing — DC Load Line and Bias Point — DC analysis of Transistor circuits — Various biasing methods of BJT — Bias Circuit Design — Thermal stability — Stability factors — Bias compensation techniques using Diode, thermistor and sensistor — Biasing BJT Switching Circuits- JFET — DC Load Line and Bias Point — Various biasing methods of JFET — JFET Bias Circuit Design — MOSFET Biasing — Biasing FET Switching Circuits.

## **UNIT II BJT AMPLIFIERS**

Small Signal Hybrid p equivalent circuit of BJT — Early effect — Analysis of CE, CC and CB amplifiers using Hybrid p equivalent circuits — AC Load Line Analysis- Darlington Amplifier — Bootstrap technique — Cascade, Cascode configurations — Differential amplifier, Basic BJT differential pair — Small signal analysis and CMRR.

#### UNIT III SINGLE STAGE FET, MOSFET AMPLIFIERS

Small Signal Hybrid p equivalent circuit of FET and MOSFET — Analysis of CS, CD and CG amplifiers using Hybrid p equivalent circuits — Basic FET differential pair- BiCMOS circuits.

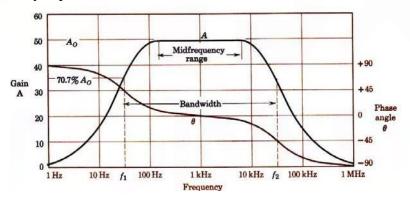

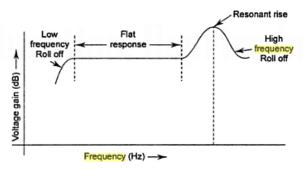

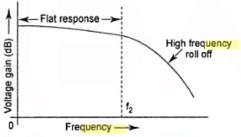

# UNIT IV FREQUENCY RESPONSE OF AMPLIFIERS

Amplifier frequency response — Frequency response of transistor amplifiers with circuit capacitors — BJT frequency response — short circuit current gain — cut off frequency — fa, fß and unity gain bandwidth — Miller effect — frequency response of FET — High frequency analysis of CE and MOSFET CS amplifier — Transistor Switching Times.

# UNIT V POWER SUPPLIES AND ELECTRONIC DEVICE TESTING

Linear mode power supply — Rectifiers — Filters — Half-Wave Rectifier Power Supply — Full- Wave Rectifier Power Supply — Voltage regulators: Voltage regulation — Linear series, shunt and switching Voltage Regulators — Over voltage protection — BJT and MOSFET — Switched mode power supply (SMPS) — Power Supply Performance and Testing — Troubleshooting and Fault Analysis, Design of Regulated DC Power Supply.

TOTAL: 45 PERIODS

# **OUTCOMES:**

After studying this course, the student should be able to:

$\bullet Acquire knowledge of <math display="inline">\clubsuit Working principles, characteristics and applications of BJT and$

FET & Frequency response characteristics of BJT and FET amplifiers

•Analyze the performance of small signal BJT and FET amplifiers - single stage and multi stage amplifiers

•Apply the knowledge gained in the design of Electronic circuits

# **TEXT BOOKS:**

1. Donald. A. Neamen, Electronic Circuits Analysis and Design, 3rd Edition, Mc Graw Hill Education (India) Private Ltd., 2010. (Unit I-IV)

2. Robert L. Boylestad and Louis Nasheresky, —Electronic Devices and Circuit Theoryl, 11thEdition, Pearson Education, 2013. (Unit V)

# **REFERENCES**

1. Millman J, Halkias.C.and Sathyabrada Jit, Electronic Devices and Circuits, 4th Edition, Mc Graw Hill Education (India) Private Ltd., 2015.

2. Salivahanan and N. Suresh Kumar, Electronic Devices and Circuits, 4th Edition, , Mc Graw Hill Education (India) Private Ltd., 2017.

3. Floyd, Electronic Devices, Ninth Edition, Pearson Education, 2012.

4. David A. Bell, Electronic Devices & Circuits, 5th Edition, Oxford University Press, 2008.

5. Anwar A. Khan and Kanchan K. Dey, A First Course on Electronics, PHI, 2006.

6. Rashid M, Microelectronics Circuits, Thomson Learning, 2007

#### UNIT II BJT AMPLIFIERS

#### 2.1 Introduction

An amplifier is used to increase the signal level. It is used to get a larger signal output from a small signal input. Assume a sinusoidal signal at the input of the amplifier. At the output, signal must remain sinusoidal in waveform with frequency same as that of input. To make the transistor work as an amplifier, it is to be biased to operate in active region. It means base-emitter junction is forward biased and base-collector junction is reverse biased.

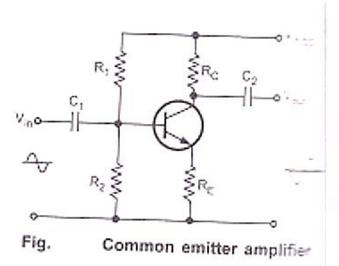

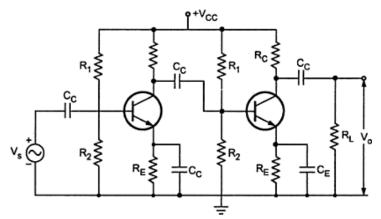

Let us consider the common emitter amplifier circuit using voltage divider bias.

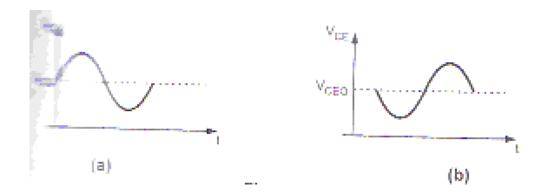

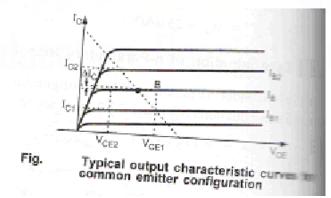

In the absence of input signal, only D.C. voltage is present in the circuit. It is known as zero signal or no signal condition or quiescent condition. D.C. collector-emitter voltage  $V_{CE}$ , D.C. collector current  $I_C$  and base current  $I_B$  is the quiescent operating point for the amplifier. Due to this base current varies sinusoidaly as shown in the below figure. Fig.  $I_{BQ}$  is quiescent DC base current

If the transistor is biased to operate in active region, output is linearly proportional to the input. The collector current is  $\beta$  times larger than the input base current in CE configuration. The collector current will also vary sinusoidally about its quiescent value I<sub>CO</sub>. The output voltage will also vary sinusoidally as shown in the below figure.

Variations in the collector current and voltage between collector and emitter due to change in base current are shown graphically with the help of load line in the above figure.

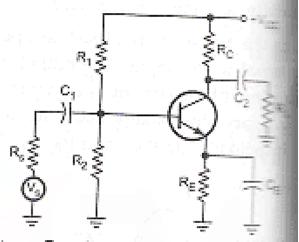

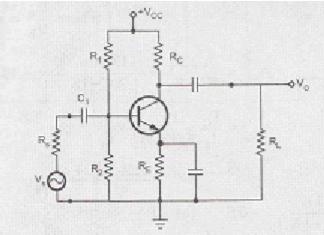

# 2.2 Common Emitter Amplifier Circuit

Fig. Practical common-emitter amplifier circuit

From above circuit, it consists of different circuit components. The functions of these components are as follows:

#### 1. Biasing Circuit:

Resistors  $R_1$ ,  $R_2$  and  $R_E$  forms the voltage divider biasing circuit for CE amplifier and it sets the proper operating point for CE amplifier.

#### 2. Input Capacitor C<sub>1</sub>:

$C_1$  couples the signal to base of the transistor. It blocks any D.C. component present in the signal and passes only A.C. signal for amplification.

#### 3. Emitter Bypass Capacitor C<sub>E</sub>:

$C_E$  is connected in parallel with emitter resistance  $R_E$  to provide a low reactance path to the amplified A.C. This will reduce the output voltage and reducing the gain value.

#### 4. Output Coupling Capacitor C<sub>2</sub>:

$C_2$  couples the output of the amplifier to the load or to the next stage of the amplifier. It blocks D.C. and passes only A.C. part of the amplified signal.

#### Need for C<sub>1</sub>, C<sub>2</sub>, and C<sub>E</sub>:

The impedance of the capacitor is given by,  $X_C = 1/(2\prod f_c)$

#### Phase reversal:

The phase relationship between the input and output voltages can be determined by considering the effect of positive and negative half cycle separately. The collector current is  $\beta$  times the base current, so the collector current will also increases. This increases the voltage drop across R<sub>C</sub>.

$V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C}$

Increase in  $I_C$  results in a drop in collector voltage  $V_{C_i}$  as  $V_{CC}$  is constant.  $V_i$  increases in a positive direction,  $V_o$  goes in negative direction and negative half cycle of output voltage can be obtained for positive half cycle at the input.

In negative half cycle of input, A.C. and D.C. voltage will oppose each other. This will reduce the base current. Accordingly collector current and drop across  $R_C$  both will reduce and it increases the output voltage. So positive half cycle at the output for negative half cycle at the input can be obtained. So there is a phase shift of 180° between input and output voltages for a common emitter amplifier.

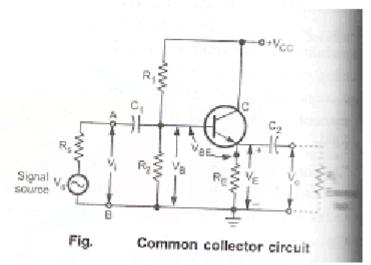

#### 2.3 Common Collector Amplifier Circuit:

From above circuit, D.C. biasing is provided by  $R_1$ ,  $R_2$  and  $R_E$ . The load resistance is capacitor coupled to the emitter terminal of the transistor. When a signal is applied to base of the transistor,  $V_B$  is increased and decreased as the signal goes positive and negative respectively.

From figure,  $VE = VB - V_{BE}$

Consider  $V_{BE}$  is constant, so the variation in  $V_B$  appears at emitter and emitter voltage  $V_E$  will vary same as base voltage  $V_B$ . In common collector circuit, emitter terminal follows the signal voltage applied to the base. It is also known as emitter follower.

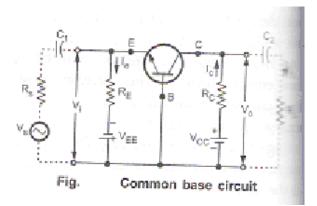

#### 2.4 Common Base Amplifier Circuit:

From above circuit, the signal source is coupled to the emitter of the transistor through  $C_1$ . The load resistance  $R_L$  is coupled to the collector of the transistor through  $C_2$ . The positive going pulse of input source increases the emitter voltage. As base voltage is constant, forward bias of emitter-base junction reduces. This reduces  $I_b$ ,  $I_c$  and drop across  $R_c$ .

$$\mathbf{V}_{\mathrm{o}} = \mathbf{V}_{\mathrm{CC}} - \mathbf{I}_{\mathrm{C}} \mathbf{R}_{\mathrm{C}}$$

Reduction in  $I_C$  results in an increase in  $V_o$ . Positive going input produces positive going output and vice versa. So there is no phase shift between input and output in common base amplifier.

# 2.5 Small Signal Low Frequency h-parameter Model:

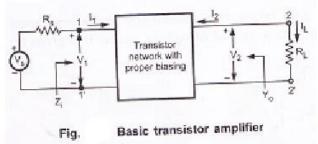

Let us consider the transistor amplifier as a block box.

Where,  $I_i$  – input current to the amplifier  $V_i$  - input voltage to the amplifier  $I_o$  – output current of the amplifier  $V_o$  – output voltage of the amplifier

Input current is an independent variable. Input voltage and output current are dependent variables. Input current and output voltage are independent variables.

$$V_{i} = f_{1} (I_{i}, V_{o})$$

$$I_{o} = f_{2} (I_{i}, V_{o})$$

This can be written in the equation form as,

$$V_i = h_{11} I_i + h_{12} V_o$$

$I_o = h_{21} I_i + h_{22} V_o$

The above equation can also be written using alphabetic notations,

$$V_{i} = h_{i} \cdot I_{i} + h_{r} \cdot V_{o}$$

$$I_{o} = h_{f} \cdot I_{i} + h_{o} \cdot V_{o}$$

# **Definitions of h-parameter:**

The parameters in the above equations are defined as follows:

$$\begin{split} h_{11} &= \frac{V_i}{I_i} \Big|_{V_{0=0}} \\ h_{12} &= \frac{V_i}{V_0} \Big|_{I_{i=0}} \\ h_{21} &= \frac{I_0}{I_i} \Big|_{V_{0=0}} \\ h_{22} &= \frac{I_0}{V_0} \Big|_{I_{i=0}} \end{split}$$

$h_{11}$  – input resistance with output short-circuited in ohms

$h_{12}$  – fraction of output voltage at input with input open circuited, it is unitless

$h_{21}$  – forward current transfer ratio or current gain with output short circuited, it is unitless

h<sub>22</sub> – output admittance with input open circuited in mhos

#### **Benefits of h-parameters:**

- 1. Real numbers at audio frequencies

- 2. Easy to measure

- 3. Can be obtained from the transistor static characteristic curve

- 4. Convenient to use in circuit analysis and design

- 5. Most of the transistor manufacturers specify the h-parameters

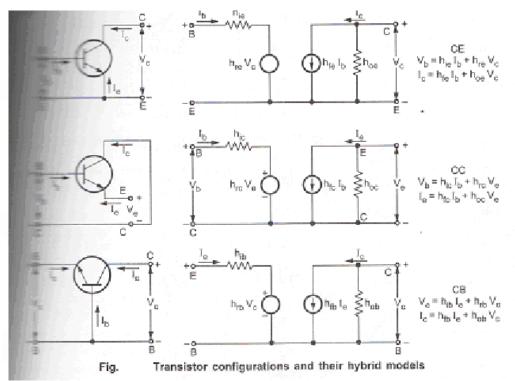

#### 2.6 h-Parameters for all three configurations:

Transistor can be represented as two port network by making anyone terminal common between input and output. There are three possible configurations in which a transistor can be used, there is a change in terminal voltage and current for different transistor configurations. To designate the type of configuration another subscript is added to h-parameters.

$h_{ie} = h_{11e}$ - input resistance in CE configuration

$h_{fb} = h_{21b}$  – short circuit current gain in CB configuration

Table: Summarizes h-parameters for all three configurations

| Parameter                    | СВ              | CE              | сс              |

|------------------------------|-----------------|-----------------|-----------------|

| nesistance                   | h <sub>ib</sub> | h <sub>ié</sub> | h <sub>ic</sub> |

| rese voltage gain            | h <sub>rb</sub> | bre             | h <sub>rs</sub> |

| covard transfer current gain | h <sub>fb</sub> | h <sub>fe</sub> | b <sub>ft</sub> |

| Supput admittance            | h <sub>ob</sub> | hoe             | ho              |

The basic circuit of hybrid model is same for all three configurations, only parameters are different.

The circuit and equations are valid for either NPN or PNP transistor and are independent of the type of load or method of biasing.

# **Determination of h-parameters from characteristics:**

Consider CE configuration, its functional relationship can be defined from the following equations:

$$V_{be} = f_1 (I_b, V_{ce})$$

$$I_c = f_2 (I_b, V_{ce})$$

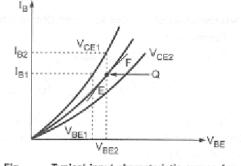

The input characteristic curve gives the relationship between input voltage  $V_{BE}$  and input current  $I_B$  for different values of output voltage  $V_{CE}$ . The following figure shows the typical input characteristic curve for CE configuration.

Fig. Typical input characteristic curves for the common emitter transistor configuration

Determination of  $h_{ie}$  and  $h_{re}$  from characteristic curve:

Parameter h<sub>ie</sub>:

$$h_{ie} = \frac{\Delta V_{BE}}{\Delta I_B} \Big|_{V_{CE \text{ constant}}} = \frac{V_{BE2} - V_{BE1}}{I_{B2} - I_{B1}}$$

**Parameter h**<sub>re</sub>:

$$\mathbf{h}_{ro} = \frac{\Delta |\mathbf{V}_{BE}|}{\Delta |\mathbf{V}_{CE}|}_{B \text{ constant}} = \frac{\mathbf{V}_{BE2} - \mathbf{V}_{BE1}}{\mathbf{V}_{CE2} - \mathbf{V}_{CE1}}$$

The output characteristic curve gives the relationship between output current  $I_C$  and output voltage  $V_{CE}$  for different values of input current  $I_B$ .

Determination of  $h_{fe}$  and  $h_{oe}$  from output characteristic curve:

Parameter h<sub>fe</sub>:

$$h_{fe} = \frac{\Delta I_C}{\Delta I_B} \Big|_{V_{CE \text{ constant}}} \approx \frac{I_{C2} - I_{C1}}{I_{B2} - I_{B1}}$$

# Parameter h<sub>oe</sub>:

$$= \frac{\Delta I_{C}}{\Delta V_{C}}\Big|_{I_{B \text{ constant}}} = \frac{I_{C2} - I_{C1}}{V_{CE2} - V_{CE1}}$$

#### 2.7 Midband analysis of BJT Single Stage Amplifiers:

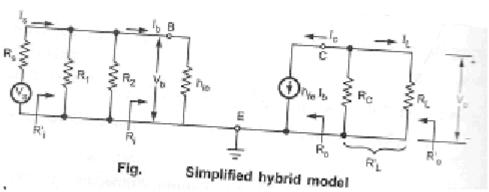

Consider the basic amplifier circuit. To form a transistor amplifier only is is necessary to connect an external load and signal source along with proper biasing.

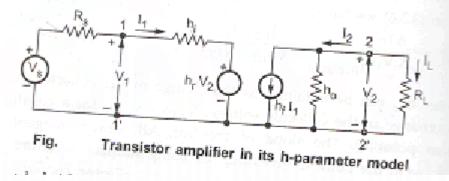

We can replace the transistor circuit as shown in the following figure.

Let us analyze the hybrid model to find current gain, input resistance, voltage gain and output resistance.

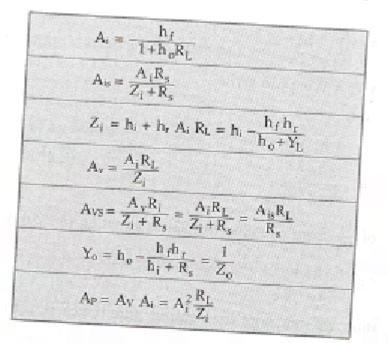

#### Current gain (A<sub>i</sub>):

It is defined as the ratio of output to input current. It is given by,

$$A_i = \frac{I_L}{I_1} = -\frac{I_2}{I_1}$$

Here  $I_L$  and  $I_2$  are equal in magnitude but opposite in sign.  $I_L$  = -I\_2 From above circuit,

$I_2 = h_f I_1 + h_0 V_2$ Substituting  $V_2 = -I_2 R_L$  in the equation, then equation become,

$$I_{2} = h_{f} I_{1} + h_{o} (-I_{2} R_{L})$$

$$I_{2} + h_{o} I_{2} R_{L} = h_{f} I_{1}$$

$$(1 + h_{o} R_{L}) I_{2} = h_{f} I_{1}$$

$$\frac{I_{2}}{I_{1}} = \frac{h_{f}}{1 + h_{o} R_{L}}$$

$$A_{i} = -\frac{I_{2}}{I_{i}} = \frac{-h_{f}}{1 + h_{o} R_{L}}$$

Current gain (A<sub>IS</sub>):

It is given by,

Fig.

From above figure, using current divider rule,

put section hybrid model

$$I_1 = \frac{I_s R_s}{Z_i + R_s}$$

$$\frac{I_i}{I_s} = \frac{R_s}{Z_i + R_s}$$

$$A_{is} = \frac{A_i R_s}{Z_i + R_s}$$

### Input Impedance (Z<sub>i</sub>):

$R_i$  is the input resistance looking into the amplifier input terminals (1, 1'). It is given by,

$$R_i = \frac{V_1}{I_1}$$

From the input circuit,

$$V_{1} = h_{i} I_{1} + h_{r} V_{2}$$

$$Z_{i} = \frac{V_{1}}{I_{1}} = \frac{h_{i} I_{1} + h_{r} V_{2}}{I_{1}}$$

$$Z_{i} = h_{i} + h_{r} \frac{V_{2}}{I_{1}}$$

Substituting  $V_2 = -I_2R_L = A_i I_1 R_L$  in the above equation,

$$Z_i = h_i + \frac{h_r A_i I_1 R_L}{I_1} = h_i + h_r A_i R_L$$

Substituting

$$A_{i} = -\frac{h_{f}}{1 + h_{o} R_{L}}$$

Then we get,

$$Z_i = h_i - \frac{h_r h_f R_L}{1 + h_o R_L}$$

Dividing numerator and denominator by R<sub>L</sub> we get,

$$Z_{i} = h_{i} - \frac{h_{r} h_{f}}{1/R_{L} + h_{o}}$$

$$Z_{i} = h_{i} - \frac{h_{r} h_{f}}{Y_{L} + h_{o}} \text{ where } Y_{L} = \frac{1}{R_{r}}$$

From this equation, note that the input impedance is a function offload impedance.

#### Voltage gain (A<sub>v</sub>):

It is the ratio of output voltage to input voltage. It is given by,

$$A_v = \frac{V_2}{V_1}$$

By substituting  $V_2 = -I_2R_L = A_i I_1 R_L$

$$A_{v} = \frac{A_{i} I_{1} R_{L}}{V_{i}} = \frac{A_{i} R_{L}}{Z_{i}}$$

$$\frac{I_{1}}{V_{1}} = \frac{1}{Z_{i}}$$

Since

# Voltage gain (A<sub>vs</sub>):

It is voltage gain including the source. It is given by,

From above figure, applying potential divider rule, then we get,

$$V_1 = \frac{Z_i}{R_s + Z_i} V_s$$

$$\frac{V_1}{V_s} = \frac{Z_i}{R_s + Z_i}$$

Substituting the value of  $V_1/V_s$  in the equation of

$$A_{vs} = A_v \times \frac{V_1}{V_S}$$

We get,

$$A_{vs} = A_v \cdot \frac{Z_i}{R_s + Z_i}$$

$$= \frac{A_i R_L}{R_s + R_i} \quad \because \quad A_v = \frac{A_i R_L}{Z_i}$$

# **Output Admittance (Y<sub>0</sub>):**

It is the ratio of output current to output voltage. It is given by,

$$Y_{a} = \frac{I_2}{V_2}$$

with  $V_a = 0$

From equation,

$$I_2 = h_f I_1 + h_o V_2$$

Dividing above equation by V<sub>2</sub>, We get,

$$\frac{I_2}{V_2} = \frac{h_f I_1}{V_2} + h_0$$

$$Y_0 = h_f \frac{I_1}{V_2} + h_0$$

From transistor amplifier in h-parameter model circuit, with  $V_s = 0$ ,

$$R_{s}I_{1} + h_{i}I_{1} + h_{r}V_{2} = 0$$

$$(R_{s} + h_{i}) I_{1} = -h_{r} V_{2}$$

$$\frac{I_{1}}{V_{2}} = \frac{-h_{r}}{R_{s} + h_{i}}$$

Substituting the value of  $I_1/V_2$  from above equation in the equation of  $Y_0$ . We obtain,

$$Y_o = h_o - \frac{h_f h_r}{h_i + R_s}$$

From this equation, note that the output admittance is a function of source resistance.

# Power gain (Ap):

It is the ratio of average power delivered to the load to the input power. Output power is given as,

$$P_2 = V_2 I_L = -V_2 I_2$$

Since the input power is  $P_1 = V_1 I_1$

The operating power gain  $A_p$  of the transistor is given as,

$$A_{P} = \frac{P_{2}}{P_{1}} = -\frac{V_{2}I_{2}}{V_{1}I_{1}} = A_{v}A_{1} = A_{1}^{2}\frac{R_{L}}{Z_{1}} \quad \forall A_{v} = \frac{A_{1}K_{L}}{Z_{1}}$$

#### **Relation between A<sub>vs</sub> and A<sub>IS</sub>:**

From equation,

$$\frac{A_i R_L}{R_s + R_i} \quad \because \quad A_v = \frac{A_i R_L}{Z_i} \qquad A_{is} = \frac{A_i R_s}{Z_i + R_s}$$

$A_{vs} =$

We have,

$$A_{vs} = \frac{A_i R_L}{Z_i + R_s} \qquad A_{is} = \frac{A_i R_s}{Z_i + R_s}$$

Taking ratio of above two equations we get,

$$\frac{A_{vs}}{A_{is}} = \frac{R_L}{R_s}$$

$$A_{vs} = A_{is} \frac{R_L}{R_s}$$

Table: Summarizes small signal analysis of a transistor amplifier

#### Method for analysis of a transistor circuit:

The analysis of transistor circuits for small signal behaviour can be made by following simple guidelines. These guidelines are,

- 1. Draw the actual circuit diagram

- 2. Replace coupling capacitors and emitter bypass capacitor by short circuit

- 3. Replace D.C. source by a short circuit

- 4. Mark the points B, E, C on the circuit diagram and locate these points as the start of the equivalent circuit

- 5. Replace the transistor by its h-parameter model

#### Problem 1:

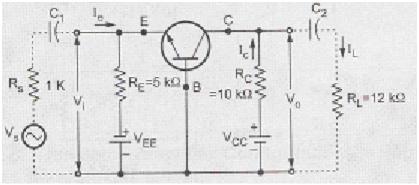

For the common base circuit shown in figure, transistor parameters are  $h_{ib} = 22\Omega$ ,  $h_{fb} = -0.98$ ,  $h_{ob} = 0.49 \mu A/V$ ,  $h_{rb} = 2.9*10^{-4}$ . Calculate the values of input resistance, output resistance, current gain and voltage gain for the given circuit.

# Solution:

Change the given figure into h-parameter equivalent model.

a) Current gain

$$(A_i) = -\frac{h_{fb}}{1 + h_{ob}R'_L}$$

$$= \frac{-(-0.98)}{1 + 0.49 \times 10^{-6} \times 5.45 \text{ K}} = 0.977$$

b) Input Resistance

c) Voltage gain

$$(A_v) = \frac{A_i R'_L}{R_i} = \frac{(0.977) \times (5.45 \text{ K})}{23.54} = 226$$

d) Overall voltage gain

$$A_{vs} = \frac{V_o}{V_s} = \frac{V_o}{V_e} \times \frac{V_e}{V_s} \text{ where } \frac{V_o}{V_e} = A_v \frac{V_e}{V_s} = \frac{R_i}{R_j' + R_w}$$

$$A_{vs} = A_v \frac{R_i'}{R_i' + R_s} = 226 \times \frac{23.43}{20.36 + 1 \text{ K}} = 5.174$$

e) Overall current gain

$$A_{i} = \frac{I_{L}}{I_{s}} = \frac{I_{L}}{I_{c}} \times \frac{I_{c}}{I_{e}} \times \frac{I_{e}}{I_{s}}$$

$$\frac{I_{L}}{I_{c}} = -\frac{R_{C}}{R_{C} + R_{L}} = -\frac{10 \text{ K}}{10 \text{ K} + 12 \text{ K}} = -0.454$$

$$e^{-\frac{I_{c}}{R_{C}}} = \frac{I_{c}}{R_{c}} = -\frac{I_{s}}{R_{c}} = -\frac{I_{s}}{Fig}$$

$$\frac{I_{c}}{I_{e}} = -A_{i} = -0.977$$

$$\frac{T_e}{I_s} = \frac{K_E}{R_E + R_i} = \frac{5 \text{ K}}{5 \text{ K} + 23.54} = 0.995$$

$$\therefore \Delta i(\text{for circuit}) = (-0.454) \times (-0.977) \times 0.996 = 0.441$$

f) Output Resistance

$$\begin{aligned} (R_{\rm o}) &= \frac{1}{h_{\rm ob} - \frac{h_{\rm fb} h_{\rm rb}}{h_{\rm ib} + R_{\rm s}'}} \\ &= \frac{1}{0.49 \times 10^{-6} - \left(\frac{-0.98 \times 2.9 \times 10^{-4}}{22 + 833.33}\right)} = 1.21 \ \mathrm{M}\Omega \end{aligned}$$

$R_{o}^{'}=R_{o}\parallel R_{L}{'}=1.21M\parallel 5.45K=5.425K\Omega$  Problem 2:

Consider a single stage CE amplifier with  $R_s = 1K\Omega$ ,  $R_L = 1.2K\Omega$ . Calculate  $A_i$ ,  $R_i$ ,  $A_v$ ,  $A_{is}$ , power gain and  $R_o$  if  $h_{ie} = 1.1k$ ,  $h_{re} = 2.5*10^{-4}$ ,  $h_{fe} = 50$  and  $h_{oe} = 25\mu A/V$ . Solution:

$$A_{i=} \frac{-h_{fe}}{1+h_{oe} R_{L}} = \frac{-50}{1+25 \times 10^{-6} \times 1.2 \times 10^{3}} = -48.54$$

Visi

$$R_{i} = \frac{h_{ie} + h_{re} A_{i} R_{L}}{100 - 2.5 \times 10^{-4} \times 48.54 \times 1200} = 1085.44 \Omega$$

$$A_{v} = \frac{A_{i} R_{L}}{R_{i}} = \frac{-48.54 \times 1200}{1085.44} = -53.663$$

$$A_{vs} = \frac{A_{v} R_{i}}{R_{i} + R_{s}} = -\frac{53.663 \times 1085.44}{1085.44 + 1000} = -27.93$$

$$A_{is} = \frac{A_i R_s}{R_i + R_s} = -\frac{48.54 \times 1000}{1085.44 + 1000} = -23.28$$

$$Y_o = R_o =$$

$$h_{ee} = \frac{h_{fe} h_{re}}{h_{ie} + R_s} = 25 \times 10^{-6} - \frac{50 \times 2.5 \times 10^{-4}}{1100 + 1000} = 19.0 \ \mu A/V$$

$$\frac{1}{Y_0} = \frac{1}{19 \times 10^{-6}} = 52.6 \text{ K}$$

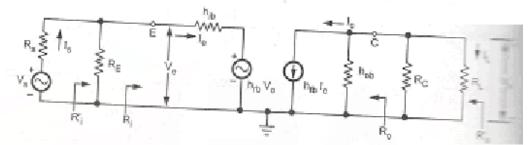

#### Problem 3:

Consider a single stage CE amplifier with  $R_s = 1k$ ,  $R_1 = 50k$ ,  $R_2 = 2k$ ,  $R_c = 2k$ ,  $R_L = 2K$ ,  $h_{ie} = 1.1k$ ,  $h_{oe} = 25\mu A/V$ ,  $h_{fe} = 50$  and  $h_{re} = 2.5*10^{-4}$  as shown in the figure. Find Ai,  $R_i$ ,  $A_v$ ,  $A_i$ ,  $A_{vs}$  and  $R_o$ .

#### Solution:

Since  $h_{oe} R_{L}^{'} = 25*10^{-6}*(2K \parallel 2K) = 0.25$ , which is less than 0.1, so use approximate analysis.

Consider the simplified hybrid model for the given circuit.

Visi

đ

a) Current gain

$$A_i) = -h_{ie} = -50$$

b) Input Impedance

$$(R_i) = h_{ie} = 1.1 \text{ K}$$

$R'_i = h_{ie} \parallel R_1 \parallel R_2 = 1.1 \text{ K} \parallel 50 \text{ K} \parallel 2 \text{ K} = 700 \text{ C}$

c) Voltage gain

$$(A_v) = \frac{A_i R_L}{R_i} = \frac{-50 \times (2K)|2K}{1.1K} = -45.45$$

d) Output Impedance

$$(R_{o}) = \frac{1}{Y_{o}} = \infty$$

$R'_{o} = R_{o} \parallel R'_{L} = \infty \parallel 2 K \parallel 2 K = 1 K$

e) Overall voltage gain

$$(A_{vs}) = \frac{V_o}{V_s} = \frac{V_o}{V_b} \times \frac{V_b}{V_s}$$

$$A_{vs} = \frac{A_v R_i'}{R_i' + R_s} = \frac{-45.45 \times 700}{700 + 1K} = -18.71$$

f) Overall current gain

ł

$$A_{i} = \frac{I_{L}}{I_{s}} = \frac{I_{L}}{I_{c}} \times \frac{I_{c}}{I_{b}} \times \frac{I_{b}}{I_{s}}$$

From above figure,

$$\frac{I_b}{I_s} = \frac{R_B}{R_B + R_i} = \frac{(50 \parallel 2)}{(50 \parallel 2) + 1.1} = 0.636$$

$$A_i \text{ (for circuit)} = \frac{I_L}{I_s} = -0.5 \times 50 \times 0.636 = -15.9$$

| <b>Comparison of</b> | <b>Transistor</b> | Configurations: |

|----------------------|-------------------|-----------------|

|----------------------|-------------------|-----------------|

| Sr.No.           | Characteristic                           | Common Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Common Emitter                                                                                                 |                                           |  |

|------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|

| 1.               | Input resistance                         | Very low (20 Ω)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | The second s | contribut contecto                        |  |

| 2.               | Output resistance                        | the second s | Low (1 kΩ)                                                                                                     | High (500 kΩ)                             |  |

| 3.               | Input current                            | Very high (1 MΩ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | High (40 kΩ)                                                                                                   | Low (50 Ω)                                |  |

| 4.               | and the second state of the second state | IE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | IB                                                                                                             | I <sub>B</sub>                            |  |

| 5.               | Output current                           | IC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | I <sub>C</sub>                                                                                                 | IF                                        |  |

| э.               | Input voltage<br>applied between         | Emitter and Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Base and Emitter                                                                                               | Base and Collector                        |  |

| 6.               | Output voltage<br>taken between          | Collector and Base                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Collector and<br>Emitter                                                                                       | Emitter and Collector                     |  |

| 7.               | Current<br>amplification factor          | $\alpha = \frac{I_C}{I_E}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\beta = \frac{I_C}{I_B}$                                                                                      | $\gamma = \frac{I_E}{I_B}$                |  |

| 8.               | Current gain                             | Less than unity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | High<br>(20 to few hundreds)                                                                                   | High<br>(20 to few hundreds)              |  |

| 9.               | Voltage gain                             | Medium                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Medium                                                                                                         | The St. Mile Trease Color Million and the |  |

| 10. Applications |                                          | As a input stage of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                | Low                                       |  |

|                  |                                          | multistage amplifier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | For audio signal<br>amplification                                                                              | For impedance matching                    |  |

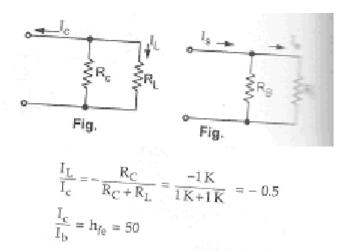

# 2.8 Introduction of Differential Amplifier

A device which accepts an input signal and produces an output signal proportional to the input, is called an amplifier. An amplifier which amplifies the difference between. the two input signals is called differential amplifier. The differential amplifier configuration is used in variety of analog circuits. The differential amplifier is an essential and basic building block in modern IC amplifier .The Integrated Circuit (IC)

technology is well known now a days, due to which the design of complex circuits become very simple. The IC version of operational amplifier is inexpensive, takes up less space and consumes less power. The differential amplifier is the basic building block of such IC operational amplifier.

Basics of Differential Amplifier

The Differential Amplifier amplifies the difference between two input voltage signal. Hence it is also called as difference amplifier.

Consider an ideal differential amplifier shown in the Fig. A

Fig. Ideal differential amplifier

$V_1$  and  $V_2$  are the two input signals while Vo is the output. Each signal is measured with respect to the ground.

In an ideal differential amplifier, the output voltage Vo is proportional to the difference between the two input signals. Hence we can write,

$V_o \propto (V_1 - V_2) \dots (-1)$

Differential Gain A<sub>d</sub>

From Equation 1 we can write,

$$\therefore \qquad V_o = A_d (V_1 - V_2) \qquad \dots (2)$$

where  $A_D$  is the constant of proportionality. The  $A_D$  is the gain with which differential amplifier amplifies the difference between two input signals. Thus it is called differential gain of the differential amplifier.

Thus, Ad = Differential gain

The difference between the two inputs  $(V_1 - V_2)$  is generally called difference voltage and denoted as Vd.

$$V_o = A_d V_d$$

Hence the differential gain can be expressed as,

...(3)

$$A_{d} = \frac{V_{o}}{V_{d}} \dots (4)$$

Generally the differential gain is expressed in its decibel (dB) value as,

$A_d = 20 \text{ Log}_{10} (A_d) \text{ in } dB \dots (5)$

# **Common Mode Gain Ac**

If we apply two input voltages which are equal in all the respects to the differential amplifier i.e. V1 = Vz then ideally the output voltage  $Vo = (V_1 - V_2) A_d$ , must be zero.But the output voltage of the practical differential amplifier not only

depends on the difference voltage but also depends on the average common level of the two inputs.

Such an average level of the two input signals is called common mode signal denoted as  $V_{\rm C}$

$$V_{c} = \frac{V_1 + V_2}{2} \dots (6)$$

Practically, the differential amplifier produces the output voltage proportional to such common mode signal, also. The gain with which it amplifies the common mode signal to produce the output is called common mode gain of the differential amplifier  $A_{C,i}$

$$V_{\rm o} = A_{\rm c} V_{\rm c} ...(7)$$

Thus there exists some finite output for V1 = V2 due to such common mode gain  $A_{C,}$  in case of practical differential amplifiers.

So the total output of any differential amplifier can be expressed as,

$$V_o = A_d V_d + A_c V_c ...(8)$$

For an ideal differential amplifier, the differential gain  $A_d$ , must be infinite while the common mode gain must be zero.

But due to mismatch in the internal circuitry, there is some output available for  $V_1 = V_2$  and gain  $A_C$  is not practically zero. The value of such common mode gain  $A_C$  very small while the value of the differential gain  $A_d$  is always very large.

#### Common Mode Rejection Ratio (CMRR)

When the same voltage is applied to both the inputs, the differential amplifier is said to be operated in a common mode configuration. Many disturbance signals, noise signal appear as a common input signal to both the input terminals of the differential amplifier. Such a common signal should be rejected by the differential amplifier. The ability of a differential amplifier to reject a common mode signal is expressed by a ratio called common mode rejection ratio denoted as CMRR. It is defined as the ratio of the differential voltage gain  $A_d$  to common mode voltage gain  $A_C$

$$CMRR = \rho = \left| \frac{A_d}{A_c} \right| \quad \dots (9)$$

CMRR in dB = 20 log  $\left|\frac{A_d}{A_c}\right| dB$  .....(10)

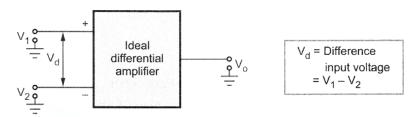

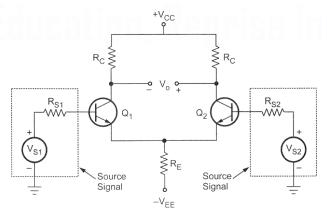

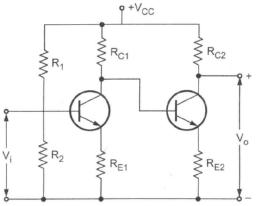

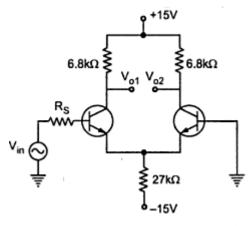

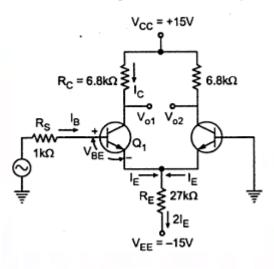

#### 2.9 Transistorised Differential Amplifier

The transistorised differential amplifier basically uses the emitter biased circuits which are identical in characteristics. Such two identical emitter biased circuits are

The two transistors Q1 and Q2 have exactly matched characteristics. The two collector

Resistors R  $_{C1}$  and R  $_{C2}$  are equal while the two emitter resistances R  $_{E1}$ and R  $_{E2}$

are equal.

$R_{C1} = R_{C2}$  and  $R_{E1} = R_{E2}$

The magnitudes of + Vcc and – V  $_{EE}$  are also same. The differential amplifier can be obtained by using such two emitter biased circuits. This is achieved by connecting emitter E1 of Q1 to the emitter E2 of Q2. Due to this, R  $_{E1}$  appears in parallel with R  $_{E2}$  and the combination can be replaced by a single resistance denoted as R  $_E$ . The base B<sub>1</sub> of Q1 is connected to the input 1 which is V  $_{S1}$  while the base B  $_2$  of Q2 is connected to the input 2 which is Vs2. The supply voltages are measured with respect to ground. The balanced output is taken between the collector C1 of Q1 and the collector C2 of Q  $_2$ . Such an amplifier is called emitter coupled differential amplifier. The two collector resistances are same hence can be denoted as R  $_C$ .

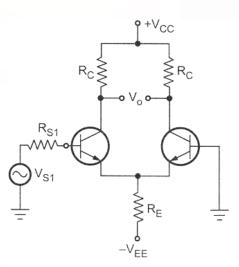

The output can be taken between two collectors or in between one of the two collectors and the ground. When the output is taken between the two collectors, none of them is grounded then it is called balanced output, double ended output or floating output. When the output is taken between any of the collectors and the ground, it is called unbalanced output or single ended output. The complete circuit diagram of such a basic dual input, balanced output differential amplifier is shown in the Fig.

Dual input, balanced output differential amplifier

As the output is taken between two output terminals, none of them is grounded, it is called balanced output differential amplifier.

Let us study the circuit operation in the two modes namely

- Differential mode operation

- Common mode operation

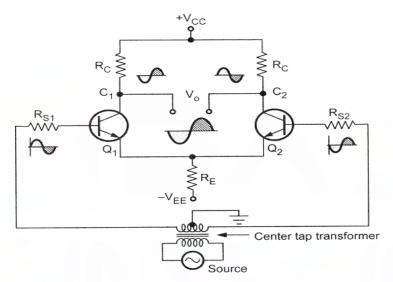

# 2.9.1 Differential Mode Operation

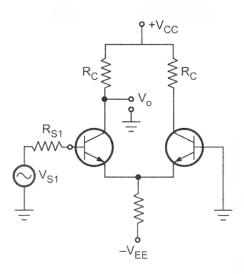

In the differential mode, the two input signals are different from each other. Consider the two input signals which are same in magnitude but 180" out of phase. These signals, with opposite phase can be obtained from the center tap transformer. The circuit used in differential mode operation is shown in the Fig..

Fig Differential mode operation

Assume that the sine wave on the base of Q<sub>1</sub> is positive going while on the base of Q<sub>2</sub> is negative going. With a positive going signal on the base of Q<sub>1</sub>, m amplified negative going signal develops on the collector of Q1. Due to positive going signal, current through R<sub>E</sub> also increases and hence a positive going wave is developed across R<sub>E</sub>. Due to negative going signal on the base of Q2, an amplified positive going signal develops on the collector of Q and a negative going signal develops across R<sub>E</sub>, because of emitter follower action of Q and 2. So signal voltages across R<sub>E</sub>, due to the effect of Q1 and Q2 are equal in magnitude and 1800 out of phase, due to matched pair of transistors. Hence these two signals cancel each other and there is no signal across the emitter resistance. Hence R<sub>E</sub> in this case does not introduce negative feedback. While Vo is the output taken across collector of Q1 and collector of Q a. The two outputs on collector L and 2 are equal in magnitude but opposite in polarity. And Vo is the difference between these two signals, e.g. +10 - (-10) = + 20.

Hence the difference output Vo is twice as large as the signal voltage from either collector to ground

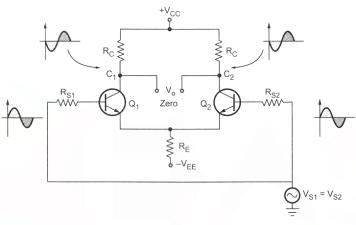

# 2.9.2 Common Mode Operation

In this mode, the signals applied to the base of Q1 and Q2 are derived from the same source. So the two signals are equal in magnitude as well as in phase. The circuit diagram is shown in the Fig.

In phase signal voltages at the bases of Q1 and Q2 causes in phase signal voltages to appear across R  $_{\rm E}$ , which add together. Hence R  $_{\rm E}$  carries a signal current and provides a negative feedback. This feedback reduces the common mode gain of differential amplifier.

Fig. Common mode operation

While the two signals causes in phase signal voltages of equal magnitude to appear across the two collectors of Q<sub>1</sub> and Q2. Now the output voltage is the difference between the two collector voltages, which are equal and also same in phase, Eg. (20) - (20) = 0. Thus the difference output Vo is almost zero, negligibly small. ideally it should be zero.

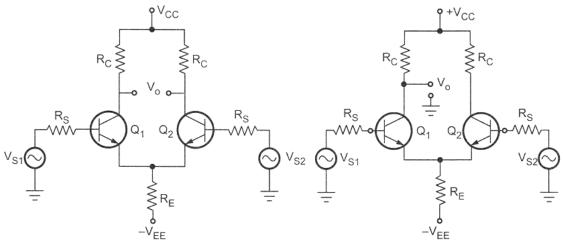

#### 2.10 Configurations of Differential Amplifier

The differential amplifier, in the difference amplifier stage in the op-amp, can be used in four configurations :

- Dual input balanced output differential amplifier.

- Dual input, unbalanced output differential amplifier.

- Single input, balanced output differential amplifier.

- Single input, unbalanced output differential amplifier.

The differential amplifier uses two transistors in common emitter configuration. If output is taken between the two collectors it is called balanced output or double ended output. While if the output is taken between one collector with respect to ground it is called unbalanced output or single ended output. If the signal is given to both the input terminals it is called dual input, while if the signal is given to only one input terminal and other terminal is grounded it is called single input or single ended input. Out of these four configurations the dual input, balanced output is the basic differential amplifier configuration. This is shown in the Fig. (a). The dual input, unbalanced output differential amplifier is shown in the Fig.(b). The single input, balanced output differential amplifier is shown in the Fig (c) and the single input, unbalanced output differential amplifier is shown in the Fig. (d).

(a) Dual input balanced output

(b) Dual input unbalanced output

(c) Single input balanced output

(d) Single input unbalanced output

# 2.11 D.C. Analysis of Differential Amplifier

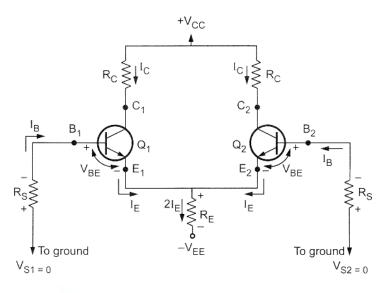

The d.c. analysis means to obtain the operating point values i.e. I <sub>C</sub>q and V <sub>CEQ</sub> for the transistors used. The supply voltages are d.c. while the input signals are a.c., so d.c equivalent circuit can be obtained simply by reducing the input a.c. signals to zero. The d.c. equivalent circuit thus obtained is shown in the Fig.. Assuming Rs <sub>1</sub> = R <sub>S2</sub>, the source resistance is simply denoted by Rs ,

Fig. D.C. equivalent circuit

The transistors Q1 and Q  $_2$  are matched transistors and hence for such a matched pair we can assume :

i) Both the transistors have the same characteristics.

ii)  $R_{E1} = R_{E2}$  hence  $R_E = R_{E1} \parallel R_{E2}$ .

iii) R  $_{C1}$  = R c  $_2$  hence denoted as R  $_C$ .

iv)  $IV_{CC}I = IV_{EE}I$  and both are measured with respect to ground.

As the two transistors are matched and circuit is symmetrical, it is enough to find out operating point I  $_{CQ}$  and V  $_{CEQ}$ , for any one of the two transistors. The same is applicable for the other transistor.

Apply-g KVL to base-emitter loop of the transistor Q1,

$$-I_{B}R_{S} - V_{BE} - 2I_{E}R_{E} + V_{EE} = 0 \dots (1)$$

$$I_{C} = \beta I_{B} \text{ and } I_{C} \cong I_{E}$$

$$I_{B} = \frac{I_{E}}{\beta} \dots (2)$$

Substituting in equation (1), we get

$$\frac{-I_E R_S}{\beta} - V_{BE} - 2I_E R_E + V_{EE} = 0$$

....(3)

#### Dept of ECE

In practice, generally  $\frac{R_S}{\beta} < < 2 R_E$

$$I_E = \frac{V_{EE} - V_{BE}}{2R_E} \dots (6)$$

Now let us determine  $V_{CE}$ . As  $I_E$  is known and  $I_E \cong I_{C'}$  we can determine the collector voltage of  $Q_1$  as

$$V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C} \qquad \dots (7)$$

Neglecting the drop across  $R_S$ , we can say that the voltage at the emitter of  $Q_1$  is approximately equal to  $-V_{BE}$ . Hence the collector to emitter voltage is

· ·

$$V_{CE} = V_C - V_E = (V_{CC} - I_C R_C) - (-V_{BE})$$

$$V_{CE} = V_{CC} + V_{BE} - I_C R_C \qquad ...(8)$$

Hence  $I_E = I_C = I_{CO}$  while  $V_{CE} = V_{CEO}$  for given values of  $V_{CC}$  and  $V_{EE}$ .

Thus for both the transistors, we can determine operating point values, using equations (6) and (.8) With the same biasing arrangement, the d.c. analysis remains same for all the four possible configurations of differential amplifier.

$$I_E = \frac{V_{EE} - V_{BE}}{\frac{R_s}{\beta} + 2R_E} \approx \frac{V_{EE} - V_{BE}}{2R_E} \approx I_{CQ}$$

$$V_{CEQ} = V_{CC} + V_{BE} - I_{CQ}R_C$$

# 2.12 A.C. Analysis of Differential Amplifier using h-Parameters

In the a.c. analysis, we will calculate the differential gain A  $_d$ , common mode gain A  $_c$ , input resistance Ri and the output resistance R  $_0$  of the differential amplifier circuit, using the h-parameters.

#### **1. Differential Gain** (A d)

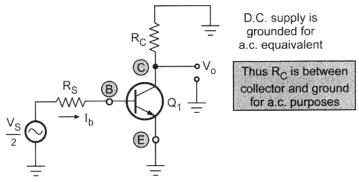

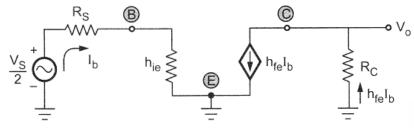

For the differential gain calculation, the two input signals must be different from each other. Let the two a.c. input signals be equal in magnitude but having 180" phase difference in between them. The magnitude of each a.c. input voltage V s<sub>1</sub> and V s<sub>2</sub> beVs /2. The two a.c. emitter currents I e<sub>1</sub> and I e<sub>2</sub> are equal in magnitude and 180' out of phase. Hence they cancel each other to get resultant a.c. current through the emitter as zero. For the a.c. purposes emitter terminal can be grounded. The a.c. small signal differential amplifier circuit with grounded emitter terminal is shown in the Fig1 As the two transistors are matched, the a.c. equivalent circuit for the other transistor is identical to the one shown in the Fig.1. Thus the circuit can be analyzed by considering only one transistor. This is called as half circuit concept of analysis. The approximate hybrid model for the above circuit can be shown as in the Fig.2, neglecting ho<sub>e</sub>,

Fig. 1 A.C. equivalent for differential operation

Fig.2 Approximate hybrid model

Applying KVL to the input loop,

$$-I_{b}R_{S} - I_{b}h_{ie} + \frac{V_{S}}{2} = 0 \qquad \dots(1)$$

$$-I_{b}(R_{S} + h_{ie}) = -\frac{V_{S}}{2}$$

$$I_{b} = \frac{V_{S}}{2(R_{S} + h_{ie})} \qquad \dots(2)$$

Applying KVL to the output loop,

$$V_{o} = -h_{fe} I_{b} R_{C} \dots (3)$$

Substituting equation (2) in equation (3),

$$V_{o} = -h_{fe} R_{C} \frac{V_{S}}{2(R_{S} + h_{ie})}$$

$$\frac{V_{o}}{V_{S}} = \frac{-h_{fe} R_{C}}{2(R_{S} + h_{ie})} \qquad \dots (4)$$

The negative sign indicates the phase difference between input and output. Now two input signal magnitudes are  $V_s$  /2 but they are opposite in polarity, as 180" out of phase.

$$V_d = V_1 - V_2 = \frac{V_S}{2} - \left(-\frac{V_S}{2}\right) = V_S$$

The **magnitude** of the differential gain  $A_d$  is

$$A_{d} = \frac{V_{o}}{V_{S}} = \frac{h_{fe} R_{C}}{2 (R_{S} + h_{ie})}$$

(For unbalanced output) ...(5)

where

$V_S = Differential input$

the expression for A  $_d$  with balanced output changes as

$$A_{d} = 2 \times \frac{h_{fe} R_{C}}{2(R_{S} + h_{ie})}$$

$$A_{d} = \frac{h_{fe} R_{C}}{(R_{S} + h_{ie})} \text{ (magnitude)} \dots 6$$

This is the differential gain for balanced output dual input differential amplifier circuit.

### 2. Common Mode Gain (A<sub>C</sub>)

Let the magnitude of both the a.c. input signals be VS and are in phase with each other. Hence the differential input Vd = 0 while the common mode input Vc is the average value of the two.

$$V_{c} = \frac{V_{1} + V_{2}}{2} = \frac{V_{S} + V_{S}}{2} \qquad \dots (7)$$

=  $V_{S}$

the output can be expressed as

$V_{o} = A_{c} V_{S} \qquad \dots (8)$

$A_{c} = \frac{V_{o}}{V_{S}} \qquad \dots (.8 (a))$

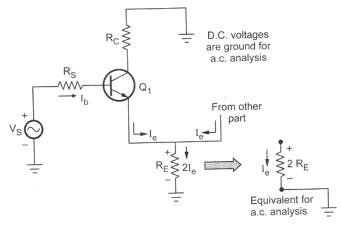

But now both the emitter currents flows through R  $_{\rm E}$  in the Same direction. Hence the total current flowing through R  $_{\rm E}$  is 2I  $_{\rm e}$ . considering only one transistor, as in the Fig

Fig. A.C. equivalent for common mode operation

The emitter resistance is shown 2 RE in the Fig

Fig. Approximate hybrid model

Current through  $R_C$  = Load current  $I_L$

Effective emitter resistance =  $2 R_E$

Current through emitter resistance =  $I_L + I_b$

Current through  $h_{oe} = (I_L - h_{fe} I_b)$

Negative sign due to the assumed direction of current. Applying KVL to the output loop,

$\frac{-(I_{L} - h_{fe} I_{b})}{h_{oe}} - 2 R_{E} (I_{L} + I_{b}) - I_{L} R_{C} = 0$

$$= -\frac{I_{L}}{h_{oe}} + \frac{h_{fe}}{h_{oe}} I_{b} - 2 R_{E} I_{L} - 2 R_{E} I_{b} - I_{L} R_{C} = 0$$

$$= I_{b} \left[ \frac{h_{fe}}{h_{oe}} - 2R_{E} \right] = I_{L} \left[ \frac{1}{h_{oe}} + 2R_{E} + R_{C} \right]$$

$$= I_{b} \left[ h_{fe} - 2R_{E} h_{oe} \right] = I_{L} \left[ 1 + h_{oe} \left( 2R_{E} + R_{C} \right) \right]$$

$$= \frac{I_{L}}{I_{b}} = \frac{\left[ h_{fe} - 2R_{E} h_{oe} \right]}{\left[ 1 + h_{oe} \left( 2R_{E} + R_{C} \right) \right]} \qquad \dots (10)$$

Substituting value of  $I_b$ , into the equation (8(b)), we get

$$V_{S} = \frac{I_{L}[1 + h_{oe} (2R_{E} + R_{C})](R_{S} + h_{ie} + 2R_{E})}{[h_{fe} - 2R_{E} h_{oe}]} + I_{L} (2R_{E})$$

$$\therefore \frac{V_{S}}{I_{L}} = \frac{[1 + h_{oe} (2R_{E} + R_{C})](R_{S} + h_{ie} + 2R_{E})}{[h_{fe} - 2R_{E} h_{oe}]} + (2R_{E})$$

Finding L.C.M. and adjusting the terms, we get

$$\therefore \frac{V_{S}}{I_{L}} = \frac{2 R_{E} (1 + h_{fe}) + R_{S} (1 + 2 R_{E} h_{oe}) + h_{ie} (1 + 2 R_{E} h_{oe}) + h_{oe} R_{C} [2 R_{E} + R_{S} + h_{ie}]}{[h_{fe} - 2 R_{E} h_{oe}]}$$

$$\therefore \frac{V_{S}}{I_{L}} = \frac{2 R_{E} (1 + h_{fe}) + (R_{S} + h_{ie}) (1 + 2 R_{E} h_{oe}) + h_{oe} R_{C} [2 R_{E} + R_{S} + h_{ie}]}{[h_{fe} - 2 R_{E} h_{oe}]}$$

$$\dots (11)$$

Neglecting the terms of  $h_{oe} R_C$  as practically  $h_{oe} R_C < < 1$ .

$$\frac{V_{S}}{I_{L}} = \frac{2 R_{E} (1 + h_{fe}) + (R_{S} + h_{ie}) (1 + 2R_{E} h_{oe})}{[h_{fe} - 2R_{E} h_{oe}]} \dots (12)$$

Substituting the value of  $I_L$ , in the equation (9)

$$V_{o} = \frac{-V_{S}(h_{fe} - 2R_{E} h_{oe}) R_{C}}{2R_{E}(1 + h_{fe}) + (R_{S} + h_{ie})(1 + 2R_{E} h_{oe})}$$

Hence the common mode gain can be written as (absorbing negative sign),

$$A_{c} = \frac{V_{o}}{V_{S}} = \frac{(2 R_{E} h_{oe} - h_{fe}) R_{C}}{2R_{E}(1 + h_{fe}) + (R_{S} + h_{ie})(1 + 2R_{E} h_{oe})} \dots (13)$$

In practice  $h_{\,oe}$  is generally neglected hence the expression for  $A_{\,c}$  can be further modified as

*.*..

....

$$A_{c} = \frac{-h_{fe} R_{C}}{R_{S} + h_{ie} + 2 R_{E} (1 + h_{fe})} \dots (14)$$

#### 2.13 Common Mode rejection Ratio (CMRR)

Once the differential and common mode gains are obtained, the expression for the CMRR can be obtained as,

$$CMRR = \left| \frac{A_{d}}{A_{c}} \right|$$

$$\therefore \qquad CMRR = \frac{R_{S} + h_{ie} + 2R_{E}(1 + h_{fe})}{(R_{S} + h_{ie})} \qquad \dots (15)$$

This is CMRR for dual input balanced output differential amplifier circuit.

#### 2.14 Techniques of Improving Input Impedance

Among three configurations (CB, CC and CE), common collector or emitter follower circuit has high input impedance. Typically it is 200 K $\Omega$  to 300 K $\Omega$ . A single stage emitter follower circuit can give input impedance upto 500 K $\Omega$ . However, the input impedance considering biasing resistors is

Figure shows the direct coupling of two stages of emitter follower significantly less. Because  $Ri' = R_1 ll R_2 ll Ri$  The input impedance of the circuit can be improved by direct coupling of two stages of emitter follower amplifier. The input impedance can be increased using two techniques :

- Using direct coupling (Darlington connection)

- Using Bootstrap technique

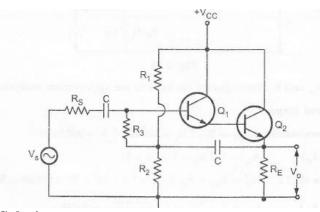

#### **2.14.1 Darlington Transistors**

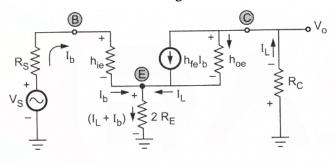

Figure shows the direct coupling of two stages of emitter follower amplifier. This cascaded connection of two emitter followers is called the Darlington connection.

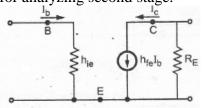

Assume that the load resistance  $R_L$  is such that  $R_L$  hoe < 0.1, therefore we can use approximate analysis method for analyzing second stage.

Figure shows approximate h-parameter (AC) equivalent circuit for common emitter configuration. The same circuit can be redrawn by making collector common to have approximate h-parameter equivalent circuit for common collector configuration.

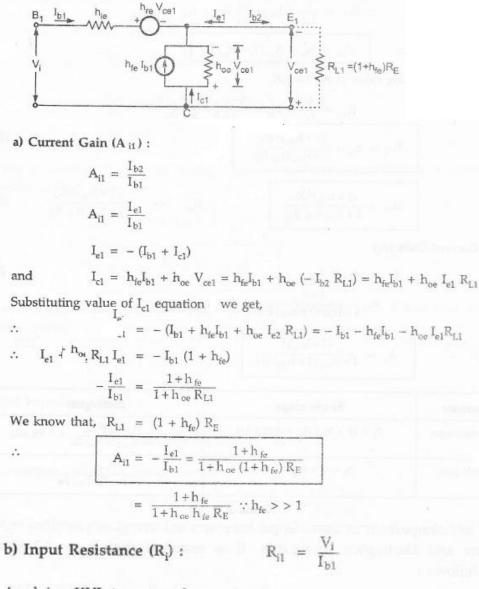

#### Analysis of second stage :

b) Input Resistance ( $R_{12}$ ) :  $R_{12} = \frac{V_2}{I_{b2}}$

Applying KVL to outer loop we get,

$$V_{2} - I_{b2} h_{ie} - I_{o} R_{E} = 0$$

$$\therefore \qquad V_{2} = I_{b2}h_{ie} + I_{o}R_{E}$$

$$\therefore \qquad \frac{V_{2}}{I_{b2}} = h_{ie} + \frac{I_{o}}{I_{b2}} R_{E}$$

$$\therefore \qquad R_{i2} = h_{ie} + A_{i2}R_{E} \quad \text{since,} \quad \frac{I_{o}}{I_{b2}} = A_{i2}$$

$$\therefore \qquad R_{i2} = h_{ie} + (1 + h_{fe}) R_{E}$$

$$R_{i2} = (1 + h_{fe}) R_{E} \quad \because h_{ie} << (1 + h_{fe}) R_{E}$$

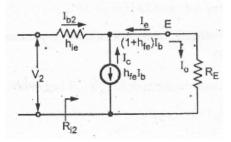

#### Analysis of first stage :

Load resistance of the first stage is the input resistance of the second stage i.e.  $R_{i2}$ . As  $R_{i2}$  is high, usually it does not meet the requirement hoe  $R_{i2} < 0.1$ , and hence we have to use the exact analysis method for analysis of the first stage.

Figure shows the h-parameter equivalent circuit for common emitter configuration.

The same circuit can be redrawn by making collector common to have h-parameter equivalent circuit for common collector for configuration.

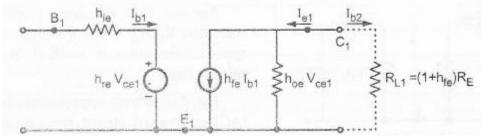

Applying KVL to output loop we get,

$$V_i - I_{b1} h_{ie} - h_{re} V_{ce1} + V_{ce1} = 0$$

$$\therefore V_r = L h$$

$$\therefore V_i = I_{b1}h_{ie} + h_{re} V_{ce1} - V_{ce1}$$

The terms  $h_{re} V_{cel}$  is negligible since  $h_{re}$  is in the order of 2.5 × 10<sup>-4</sup>

$$= I_{b1}h_{ie} - (-I_{b2}R_{L1}) = I_{b1}h_{ie} + I_{b2}R_{L1}$$

$$\therefore R_{i1} = \frac{V_i}{I_{b1}} = h_{ie} + \frac{I_{b2}}{I_{b1}}R_{L1} = h_{ie} + A_{i1}R_{L1}$$

$$R_{i1} = h_{ie} + A_{i1} (1 + h_{fe}) R_E$$

Jeppiaar Institute of Technology

2021-2022

Substituting value of A<sub>i1</sub> we get,

$$R_{i1} = \frac{V_i}{I_{b1}} = h_{ie} + \frac{(1+h_{fe})(1+h_{fe})R_E}{1+h_{oe}h_{fe}R_E}$$

$$\therefore \qquad R_{i1} = h_{ie} + \frac{(1+h_{fe})^2R_E}{1+h_{oe}h_{fe}R_E}$$

$$\therefore \qquad R_{i1} = \frac{(1+h_{fe})^2R_E}{1+h_{oe}h_{fe}R_E} \qquad \because h_{ie} \qquad << \qquad \frac{(1+h_{fe})^2R_E}{1+h_{oe}h_{fe}R_E}$$

**Overall current gain(Ai)**

$$A_{i} = A_{i1} \times A_{i2}$$

$$= \frac{1 + h_{fe}}{1 + h_{oe} (1 + h_{fe}) R_{E}} \times (1 + h_{fe})$$

$$\therefore \qquad A_{i} = \frac{(1 + h_{fe})^{2}}{1 + h_{oe} (1 + h_{fe}) R_{E}}$$

From table, we can say that Darlington connection improves input impedance as well as current gain of the circuit

## Overall Voltage gain

| Parameter        | Single stage                              | Darlington                                                                                    |

|------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------|

| Input resistance | $R_i = (1 + h_{fe}) R_E = 168.3 k\Omega$  | $R_{i} = \frac{(1+h_{ie})^{2} R_{E}}{1+h_{oe} (1+h_{fe}) R_{E}} \approx 1.65 \text{ M}\Omega$ |

| Current gain     | A <sub>i</sub> = 1 + h <sub>fe</sub> = 51 | $A_{i} = \frac{(1 + h_{fe})^{2}}{1 + h_{oe} (1 + h_{fe}) R_{E}} \approx 500$                  |

We know that

$$A_{v} = \frac{A_{i}R_{L}}{R_{i}}$$

By subtracting 1 on both sides we get

$$1 - A_{v} = 1 - \frac{A_{i}R_{L}}{R_{i}}$$

$$\therefore \qquad 1 - A_{v} = \frac{R_{i} - A_{i}R_{L}}{R_{i}} = \frac{h_{ic} + h_{rc}A_{i}R_{i} - A_{i}R_{L}}{R_{i}}$$

$$= \frac{h_{ie}}{R_{i}} \text{ since } h_{ic} = h_{ie} \text{ and } h_{rc} = 1 - h_{re} \approx 1$$

$$\therefore \qquad A_{v} = 1 - \frac{h_{ie}}{R_{i}}$$

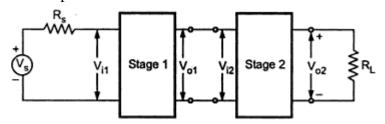

We know that the overall voltage gain in multistage amplifier is a product of individual voltage gain

$$\therefore \qquad \mathbf{A}_{\mathbf{v}} = \mathbf{A}_{\mathbf{v}1} \mathbf{A}_{\mathbf{v}2} = \left(1 - \frac{\mathbf{h}_{ie}}{\mathbf{R}_{i1}}\right) \left(1 - \frac{\mathbf{h}_{ie}}{\mathbf{R}_{i2}}\right)$$

$$\therefore \qquad \mathbf{A}_{\mathbf{v}} = 1 - \frac{\mathbf{h}_{ie}}{\mathbf{R}_{i2}} - \frac{\mathbf{h}_{ie}}{\mathbf{R}_{i1}} + \frac{\mathbf{h}_{ie}^2}{\mathbf{R}_{i1}\mathbf{R}_{i2}}$$

As we know, input resistance Ri1 >> Ri2 we can neglect term 3 and term 4 in the above equation.

$$\therefore \qquad A_{\rm v} \approx 1 - \frac{h_{\rm ie}}{R_{\rm i2}}$$

Output Impedance (Ro<sub>2</sub>):

$$R_o = \frac{1}{Output admittance} = \frac{1}{Y_o}$$

From equation, Yo of the transistor is given as

$$Y_o = Y_{o1} = h_{oc} - \frac{h_{fc} \cdot h_{rc}}{h_{ic} + R_s} = h_{oe} - \frac{-(1 + h_{fe})}{h_{ie} + R_s}$$

Since

$$h_{oc} = h_{oe},$$

$$h_{fr} = -(1 + h_{fe})$$

And

$$\begin{split} h_{ic} &= h_{ie} \\ Y_{o1} &= h_{oe} + \frac{(1+h_{fe})}{h_{ie} + R_s} \\ Y_{o1} &= \frac{1+h_{fe}}{h_{ic} + R_s} \\ \ddots & h_{oe} << \frac{(1+h_{fe})}{h_{ic} + R_s} \\ \therefore & R_{o1} = \frac{1}{Y_{o1}} \\ \vdots & R_{o1} = \frac{h_{ie1} + R_s}{1+h_{fe}} \end{split}$$

Looking at Figure we can see that the  $R_{i1}$  of the first stage is the source resistance for second stage, i.e.  $R_{S2} = R_{O1}$

$$\therefore \qquad R_{o2} = \frac{R_{s2} + h_{ie2}}{1 + h_{fe}} = \frac{\left(\frac{h_{ie1} + R_s}{1 + h_{fe}}\right) + h_{ie2}}{1 + h_{fe}}$$

$$\therefore \qquad R_{o2} = \frac{h_{ie1} + R_s}{(1 + h_{fe})^2} + \frac{h_{ie2}}{1 + h_{fe}}$$

2021-2022

Since the current in  $T_2$  is  $1 + h_{fe}$  times the current in  $T_1$ ,  $h_{ie1} \approx (1 + h_{fe})h_{ie2}$  substituting this value of  $h_{ie1}$  in equation 15 we get,

$$R_{o2} = \frac{(1+h_{fe})h_{ie2} + R_s}{(1+h_{fe})^2} + \frac{h_{ie2}}{1+h_{fe}} = \frac{h_{ie2}}{1+h_{fe}} + \frac{R_s}{(1+h_{fe})^2} + \frac{h_{ie2}}{1+h_{fe}}$$

$$R_{o2} = \frac{R_s}{(1+h_{fe})^2} + \frac{2h_{ie2}}{(1+h_{fe})}$$

#### **Key Point:**

...

- In above analysis we have assumed that the h-parameter of T1 and T2 are identical,

- From the above analysis we have seen that Darlington connection of two transistorimproves current gain and input resistance of the circuit.

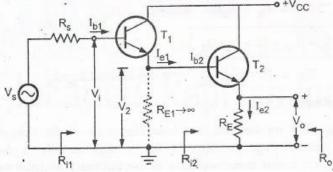

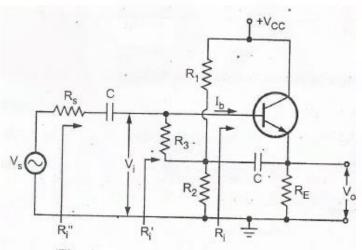

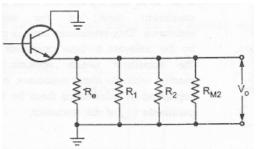

### 2.14.2 Bootstrap Emitter Follower

In emitter follower, the input resistance of the amplifier is reduced because of the shunting effect of the biasing resistors. To overcome this problem the emitter follower circuit is modified, as shown in the Figure. Here, two additional components are used, resistance R, and capacitor C. The capacitor, is connected between the emitter and the junction of R1,R2 and R3.

For d.c. signal, capacitor C acts as a open circuit and therefore resistance R1,R2 and R3 provides necessary biasing to keep the transistor in active region.

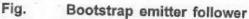

For ac signal, the capacitor acts as a short circuit. Its value is chosen such that it provides very low reactance nearly short circuit at lowest operating frequency. Hence for ac, the bottom of R3 is effectively connected to the output(the emitter), whereas the top of R3 is at the -input. (the base). In other words, R3 is connected between input node and output node. For such connection effective input resistance is given by Miller's theorem. The two components are

$$\frac{Z}{1-K}$$

and  $\frac{Z \cdot K}{K-1}$

R3 is the impedance between output voltage and input voltage and K is the voltage gain.

These are

$$R_{M1} = \frac{R_3}{1-A_v}$$

and  $R_{M2} = \frac{R_3 A_v}{A_v - 1}$

Since, for an emitter follower, Av, approaches unity, then R<sub>M2</sub> becomes extremely large.

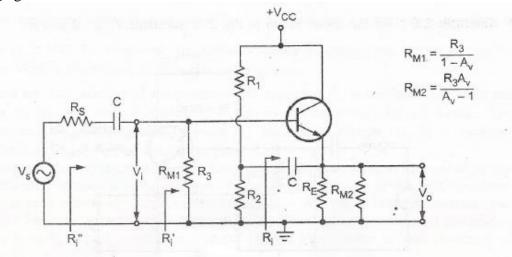

$$R'_i = R_i \parallel R_M$$

$R_i = h_{ie} + (1 + h_{fe}) R_E$

The above effect, when Av tends to unity is called bootstrapping. The name arises from the fact that, if one end of the resistor  $R_3$  changes in voltage, the other end of  $R_3$  moves through the same potential difference; it is as if  $R_3$  is pulling itself up by its bootstraps.

The effective load on the emitter follower can be given as

$\mathbf{R}_{\mathrm{L~eff}} = \mathbf{R}_{\mathrm{E}} \parallel \mathbf{R}_{1} \parallel \mathbf{R}_{2} \parallel \mathbf{R}_{\mathrm{M2}}$

Because of the capacitor, biasing resistances R1 and R2, come on output side shunting effective load resistance. The resistance  $R_{M2}$  is very large and hence it is often neglected.

$$\therefore \quad \mathbf{R}_{\mathrm{L eff}} = \mathbf{R}_{\mathrm{E}} \parallel \mathbf{R}_{1} \parallel \mathbf{R}_{2}$$

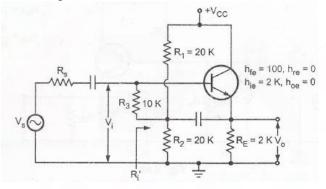

Problem

1. For the circuit shown in Figure calculate R<sub>Leff</sub>, Ri, and Ri'

Solution : Here,  $R_{Leff} = R_1 \parallel R_2 \parallel R_E = 20 \text{ K} \parallel 20 \text{ K} \parallel 2 \text{ K} = 1.67 \text{ k}\Omega$   $R_i = h_{ie} + (1 + h_{fe}) R_{L eff} = 2 \times 10^3 + (1 + 100) \times 1.67 \times 10^3 = 170.67 \text{ k}\Omega$  $R'_1 = R_1 \parallel \frac{R_3}{1 - A_v}$

where

$A_{v} = 1 - \frac{h_{ie}}{R_{i}} = 1 - \frac{2 \times 10^{3}}{170.67 \times 10^{3}} = 0.988$

$R_{1}^{\prime} = 170.67 \times 10^{3} \parallel \frac{10 \times 10^{3}}{1 - 0.988} = 170.67 \times 10^{3} \parallel 833.33 \times 10^{3} = 141.66 \ k\Omega$

# 2. Analyze the following circuit for the following values of resistors and h-parameters

$R_s = 10 \text{ k}$ ,  $R_1 = 100 \text{ k}$ ,  $R_2 = 10 \text{ k}$ ,  $R_3 = 50 \text{ k}$ ,  $R_E = 1 \text{ k}$ ,  $h_{ie} = 1 \text{ k}\Omega$ ,  $h_{fe} = 100$ ,  $h_{re} = 2.4 \times 10^{-4}$  and  $h_{oe} = 2.5 \times 10^{-5} \text{ A/V}$ .

### **Solution** Analysis of second stage

The load resistance R12 for second stage is given by

$R_{L2} = R_E || R_1 || R_2 || R_{M2}$

By Miller's theorem  $R_{M2}$  is given as  $R_{M2} = \frac{R_3 A_v}{A_v - 1}$ . As  $A_v$  approaches to 1 in CC amplifier  $R_{M2}$  is very high. Hence  $R_{L2}$  can be approximated as,

$R_{L2} = R_E || R_1 || R_2 = 1 K || 100 K || 10 K = 900.9 \Omega$

:.  $h_{oe}R_{1.2} = 2.5 \times 10^{-5} \times 900.9 = 0.0225$

Since  $h_{oe}R_{L2} < 0.1$  we can use the approximate analysis.

#### Analysis for second stage (common collector amplifier).

| a) Current gain (A i2)                 | $A_{i2} = 1 + h_{fe} = 1 + 100 = 101$                                           |

|----------------------------------------|---------------------------------------------------------------------------------|

| b) Input resistance (R <sub>i2</sub> ) | $R_{i2} = h_{ie} + (1 + h_{fe}) R_{L2} = 1 K + (1 + 100) 900.9 = 91.99 k\Omega$ |

- c) Voltage gain (A<sub>v2</sub>)  $A_{v2} = 1 \frac{h_{ic}}{R_{i2}} = 1 \frac{1K}{91.99K} = 0.989$

- Analysis of first stage

For first stage  $R_{L1} = R_{i2} = 91.99 \text{ k}\Omega$

:.

$$h_{00}R_{L1} = 2.5 \times 10^{-5} \times 91.99 \times 10^{-3} = 2.299$$

Since  $h_{oe}R_{L1} > 0.1$  we have to use the exact analysis for the first stage.